随着 RISC-V 架构在嵌入式系统、云计算等领域的广泛应用,硬件级安全隔离需求日益凸显。

本文基于 WorldGuard RVIA 规范(版本 v0.4),系统阐述了 WorldGuard 技术的设计理念、核心架构与实现机制。

WorldGuard 通过物理地址访问约束构建独立的 “World” 执行上下文,利用硬件世界标识符(WID)实现多 World 间的隔离,并结合 RISC-V 指令集架构(ISA)扩展与非 ISA 硬件组件,形成完整的权限控制体系。

规范定义了 3 级 ISA 扩展支持(无扩展、Smwg 扩展、Smwgd/Sswg 扩展)与通用 WG 检查器等硬件模块,明确了事务处理流程与权限违规响应机制。

该技术可由可信执行环境(TEE)在系统启动时完成配置,且支持 2-8 个 World 的隔离需求,为 RISC-V 平台提供低成本、高安全性的硬件隔离解决方案。

QEMU 上游最近开始支持 RISC-V 的 WorldGuard 扩展(提案),趁这个机会,我们详细解读一下这个扩展。

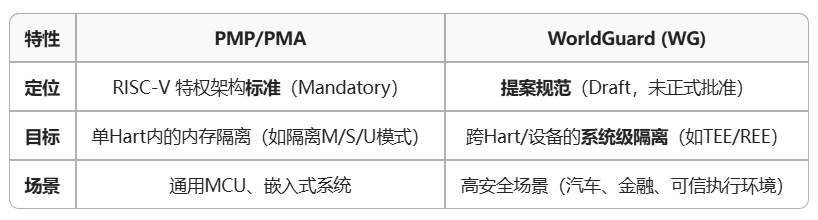

与 PMP/PMA 不同的是, WorldGuard (WG) 主要提供跨 Hart / 设备的系统级别隔离。以下是核心差异的对比:

下面是对 WorldGuard 扩展的具体解读。

点击我听 ima 播客:https://ima.qq.com/share/#/ai-chat/XiJ055pOp

1. 引言

1.1 技术背景

RISC-V 架构凭借其开源性、可扩展性与灵活性,已成为处理器设计的重要标准。

然而,随着应用场景的复杂化,不同执行上下文间的安全隔离需求愈发迫切 —— 例如,在同一硬件平台上同时运行可信系统与不可信应用时,需防止不可信应用越权访问可信资源。

传统软件级隔离方案(如虚拟内存、沙箱)存在性能开销大、依赖软件栈安全性等问题,而硬件级隔离技术可通过硬件机制直接约束资源访问,具备更高的安全性与效率。

1.2 WorldGuard 技术定位

WorldGuard(简称 WG)是针对 RISC-V 架构提出的硬件隔离技术提案,目前处于 RVIA(RISC-V International Association)标准制定的初始阶段。

其核心目标是通过物理地址访问控制,在硬件层面构建独立的执行单元(即 “World”),实现不同 World 间的资源隔离,同时兼顾硬件成本与配置灵活性。

与其他硬件隔离技术(如 RISC-V PMP)相比,WorldGuard 支持多 World 的全局权限管理,且配置通常在系统启动时完成,更适用于对隔离稳定性要求较高的场景。

1.3 文档范围

本文基于 WorldGuard RVIA 规范 v0.4 版本,重点分析技术的核心概念、ISA 扩展设计、非 ISA 硬件组件及事务处理流程,为后续技术实现与标准化提供参考。

2. WorldGuard 核心概念与整体架构

2.1 核心定义

2.1.1 World

World 是 WorldGuard 技术的基本隔离单元,定义为包含代理(Agent) 与资源(Resource) 的执行上下文:

-

代理:可发起物理地址事务的硬件实体,包括 hart(处理器核心)与外设设备,每个代理上下文同时仅属于一个 World;

-

资源:可响应物理地址事务的硬件实体,包括内存与外设,通过系统物理地址唯一标识,支持在多个 World 间共享(各 World 权限独立)。

2.1.2 硬件世界标识符(WID)

每个 World 由唯一的 WID 标识,平台支持的最大 WID 数量为 NWorlds。考虑到硬件成本,规范建议 NWorlds 取值为 2-8(需 1-3 位二进制表示),具体数量由平台设计决定。

2.1.3 可信执行环境(TEE)

TEE 是负责 World 配置的可信组件,通常在系统启动 / 复位时完成代理与资源到 World 的分配,且配置一旦生效,除非系统复位,否则不支持动态修改(当前规范不将 “运行时动态配置” 作为设计目标)。

2.2 整体架构

WorldGuard 的整体架构分为两大核心部分:

-

RISC-V ISA 扩展:通过新增控制状态寄存器(CSR),实现 hart 特权模式与 WID 的关联,支持不同特权模式的 World 切换;

-

非 ISA 硬件组件:包括 WG 标记器(为代理事务添加 WID)与 WG 检查器(检查事务权限),实现物理地址访问的硬件级权限校验。

两者协同工作,形成 “事务标记 - 权限检查 - 结果响应” 的完整流程:

-

代理发起物理地址事务,WG 标记器为事务添加当前 World 的 WID;

-

事务在总线层级传播时,WG 检查器校验目标资源对该 WID 的访问权限;

-

若权限通过,事务正常完成;若权限违规,事务被终止或修改,并按规则报告错误。

3. RISC-V ISA WorldGuard 扩展

为支持 hart 对 World 的灵活管理,规范定义了 3 级 ISA 扩展支持,各级扩展的功能与依赖关系如下表所示。

3.1 3 级 ISA 扩展支持体系

| 支持等级 | 核心功能 | 依赖条件 | 关键组件 |

|---|---|---|---|

| 1 级(无扩展) | 所有特权模式共享固定 WID,hart 复位后属于单个 World | 无需 ISA 扩展 | - |

| 2 级(Smwg 扩展) | M 模式可控制低特权模式(如 [H] S、U)的 WID | hart 至少支持 2 种特权模式 | 新增 mlwid CSR |

| 3 级(Smwgd/Sswg 扩展) | M 模式可委托 [H] S 模式控制更低特权模式(如 U、VS、VU)的 WID | 依赖 Smwg 扩展 | 新增 mwiddeleg CSR(Smwgd)、slwid CSR(Sswg) |

3.2 关键 CSR 设计

CSR(Control and Status Register)是 ISA 扩展的核心,用于存储 WID 配置与委托信息,规范定义的关键 CSR 如下表所示。

| 寄存器名称 | 位宽 | 访问权限 | 提议地址 | 功能描述 | 关键特性 |

|---|---|---|---|---|---|

| mlwid | XLEN | M 模式读写 | 0x390 | 设置低特权模式使用的 WID | 1. 有效位:Ceil (Log₂NWorlds) 个最低位,其余位为 0; 2. WARL 属性:写入非法 WID 时,返回最小合法 WID; 3. 复位要求:复位时需持有可分配给低特权模式的 WID |

| mwiddeleg | XLEN | M 模式读写 | 0x748 | 存储委托给 [H] S 模式的 WID 集合(位向量) | 1. 有效位:NWorlds 个最低位,位 i 对应 WID i; 2. WARL 属性:仅可设置平台允许委托的 WID 位; 3. 复位值:复位时为 0,此时 Sswg 扩展禁用 |

| slwid | XLEN | [H] S 模式读写 | 0x190 | 设置 U、VS、VU 模式使用的 WID | 1. 有效位:同 mlwid; 2. WARL 属性:仅可写入 mwiddeleg 允许的 WID; 3. 启用条件:mwiddeleg 非 0 时启用,否则访问触发非法指令异常 |

3.3 特殊规则与兼容性设计

3.3.1 内存访问标记规则

所有内存访问(包括指令获取、页表遍历等隐式访问)均需标记当前 World 的 WID,且指令获取在权限检查中被视为 “读操作”—— 这是因为总线通常不区分指令获取与数据读,需统一权限校验逻辑。

3.3.2 WID 修改限制

-

特权模式无法修改自身的 WID,仅高特权模式可修改低特权模式的 WID(如 M 模式修改 [H] S 模式,[H] S 模式修改 U 模式);

-

M 模式的 WID 由外部环境设置,复位期间不变化,且不同 hart 的 M 模式可使用不同 WID。

3.3.3 虚拟内存兼容性

若系统支持请求分页虚拟内存,地址转换缓存(如 TLB)需为每个 WID 单独缓存转换结果,避免不同 World 的地址转换冲突。规范建议:在写入 mlwid、mwiddeleg 或 slwid 时,刷新地址转换缓存,以确保配置生效。

4. 非 ISA WorldGuard 硬件组件

非 ISA 硬件组件是 WorldGuard 权限校验的执行层,包括 WG 标记器与 WG 检查器,其中 “通用 WG 检查器” 是规范定义的核心模块,支持灵活的地址范围与权限配置。

4.1 组件通用设计原则

-

定制化支持:WG 标记器可针对特定设备代理定制(如外设专用标记逻辑),WG 检查器可针对特定资源定制(如内存与外设的不同校验策略),以降低硬件成本;

-

配置安全性:动态配置状态(如检查器规则)需在复位时初始化至 “安全状态”(如禁用所有权限),且支持初始化后锁定(防止未授权修改),锁定状态仅可通过系统复位解除。

4.2 通用 WG 检查器设计

通用 WG 检查器的核心功能是监控固定物理地址范围,通过可编程 “规则插槽” 配置各 World 的访问权限,适用于需要灵活权限管理的场景(如内存区域隔离)。

4.2.1 基本功能与地址范围

-

检查器监控的地址范围通常为自然对齐的 NAPOT 区域(Naturally Aligned Power-Of-Two),便于硬件电路实现;

-

检查器的地址范围可大于其背后设备的实际地址范围(如设备地址范围为 0x1000_0000-0x2FFF_FFFF,检查器范围可设为 0x0_0000_0000-0x3_FFFF_FFFF),未路由至设备的地址不影响校验逻辑。

4.2.2 配置寄存器内存映射

检查器的配置寄存器映射到独立的物理地址区域,仅可信软件可访问,支持 32b 读写(也支持更宽访问以提升配置效率)。关键配置寄存器如下表所示:

| 偏移量(字节) | 大小(字节) | 访问类型 | 寄存器名称 | 功能描述 |

|---|---|---|---|---|

| 0x00 | 4 | 只读 | vendor | 厂商 ID,标识检查器供应商 |

| 0x04 | 4 | 只读 | impid | 实现版本,标识检查器硬件版本 |

| 0x08 | 4 | 只读 | nslots | 规则插槽数量(≥1,slot [0] 不计入) |

| 0x10 | 8 | 读写 | errcause | 记录权限违规信息(如 WID、访问类型) |

| 0x18 | 8 | 读写 | erraddr | 记录权限违规的物理地址(右移 2 位存储) |

| 0x20 | 32*(nslots+1) | 读写 | slot[0..nslots] | 规则插槽数组,存储地址范围与权限配置 |

4.2.3 规则插槽格式与配置

每个规则插槽占用 32 字节,包含地址、权限与配置信息,格式如下表所示:

| 偏移量(字节) | 大小(字节) | 字段名称 | 功能描述 |

|---|---|---|---|

| 0x00 | 4 | addr[33:2] | 规则地址低 32 位 |

| 0x04 | 4 | addr[65:34] | 规则地址高 32 位(仅 RV64 系统有效) |

| 0x08 | 8 | perm[nWorlds-1:0] | 各 World 的权限,每个 WID 占 2 位(位 2i = 读,位 2i+1 = 写) |

| 0x10 | 4 | cfg | 规则配置,含地址范围、错误报告、锁定位 |

其中,cfg 寄存器是规则配置的核心,关键位段定义如下:

- A [1:0](位 1:0):地址范围类型,支持 OFF(禁用)、TOR(范围顶部)、NA4(4 字节对齐)、NAPOT(≥8 字节幂次对齐);

- ER(位 8)/EW(位 9):读 / 写权限违规时是否报告总线错误;

- IR(位 10)/IW(位 11):读 / 写权限违规时是否触发中断;

- L(位 31):锁定位,设置后插槽配置不可修改(需复位解除)。

4.2.4 错误报告机制

检查器通过 errcause 与 erraddr 寄存器记录权限违规,核心逻辑如下:

-

erraddr:存储违规物理地址,右移 2 位(addr [65:2]),确保 RV32 系统可存储 34 位地址;

-

errcause:记录违规细节,包括触发违规的 WID(位 7:0)、访问类型(位 8 = 读,位 9 = 写)、是否生成总线错误(位 62)与中断(位 63);

-

报告限制:仅当 errcause 的总线错误位(be)与中断位(ip)均为 0 时,新违规才更新寄存器;软件需清除这两位,才能重新启用错误报告。

5. 事务处理与权限违规响应

5.1 正常事务处理流程

当代理(hart / 设备)发起物理地址事务时,处理流程如下:

-

WG 标记器为事务添加当前 World 的 WID;

-

事务通过总线传播,途经的 WG 检查器校验目标地址对该 WID 的权限;

-

若存在至少一个规则允许该访问(权限 accretive,即多规则重叠时取 “允许” 交集),事务正常完成;

-

若所有规则均拒绝访问,触发权限违规处理。

5.2 权限违规响应策略

权限违规时,检查器需确保 World 隔离不被破坏,响应策略分为两类:

- 事务处理:

-

写操作:忽略对目标资源的写入,不修改资源数据;

-

读操作:返回与目标资源无关的 “无害数据”(通常为 0),避免泄露可信信息。

- 错误报告:

-

若规则配置 ER/EW 位,向总线返回错误响应;

-

若规则配置 IR/IW 位,触发中断并更新 errcause/erraddr 寄存器;

-

部分场景下(如无法向发起代理报告错误),仅通过其他代理(如管理 hart)报告违规。

6. 版本历史与未来展望

6.1 版本迭代

WorldGuard RVIA 规范 v0.4 是当前最新版本,其迭代历史如下:

-

版本 0.1(2022-10-31):初始草案,基于 WorldGuard HAS Specification 1.1;

-

版本 0.2(2022-11-20):第二版草案,优化后拟捐赠给 RVIA;

-

版本 0.3-draft(2022-11-22):开发中的第三版草案;

-

版本 0.3(2023-04-03):正式捐赠给 RVIA;

-

版本 0.4(2023-04-27):澄清检查器操作逻辑,支持非 32b 访问,移除 NAPOT 可选性要求。

6.2 未来挑战与方向

当前规范仍处于初始阶段,未来需解决的关键问题包括:

-

动态配置支持:当前规范不支持运行时动态修改 World 配置,需探索低成本的动态配置机制,以适应虚拟化等场景;

-

多平台兼容性:规范允许平台特定的实现(如总线 WID 传播方式),需制定兼容性测试标准,确保不同厂商硬件的互操作性;

-

性能优化:权限检查可能引入总线延迟,需研究并行校验、缓存优化等技术,降低性能开销。

7. 结论

WorldGuard 技术通过 “World 隔离 + WID 标记 + 硬件校验” 的三层设计,为 RISC-V 架构提供了硬件级安全隔离解决方案。

其 ISA 扩展支持灵活的特权模式 - WID 关联,非 ISA 硬件组件实现高效的权限校验,且整体设计兼顾硬件成本与安全性。

尽管当前规范仍处于标准化初期,但其核心架构已具备明确的应用场景(如嵌入式安全、云原生隔离),为后续 RISC-V 平台的安全增强提供了重要参考。

未来,随着动态配置、兼容性测试等问题的解决,WorldGuard 有望成为 RISC-V 架构的核心安全标准之一。

参考文献

[1] WorldGuard RVIA Specification v0.4, 2023.

[2] RISC-V Privileged Specification, Ratified Specifications - RISC-V International.